# OpenPICs Status Update openPICs WP3 PHX-0574

MARCEL VAN DER VIIET

APR 4<sup>TH</sup> 2018

© COPYRIGHT 2017-2018 SYNOPSYS, INC. THIS SYNOPSYS MANUAL AND ALL ASSOCIATED DOCUMENTATION ARE PROPRIETARY TO SYNOPSYS, INC. AND MAY ONLY BE USED PURSUANT TO THE TERMS AND CONDITIONS OF A WRITTEN LICENSE AGREEMENT WITH SYNOPSYS, INC. ALL OTHER USE, REPRODUCTION, MODIFICATION, OR DISTRIBUTION OF THE SYNOPSYS MANUAL OR THE ASSOCIATED DOCUMENTATION IS STRICTLY PROHIBITED.

# Main focus points PhoeniX

- Design Flow WP3.4.DF

- Execution Flow WP3.4.EF

- PDAFlow Template WP3.4.PDA

- Design Rule Checks WP3.4.DRC

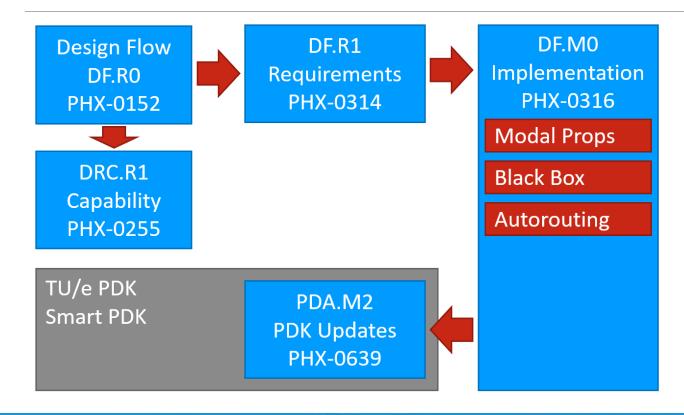

# Design Flow

# Design Flow WP3.4.DF

#### Deliverables

- R0 Mar 17: Design Flow document (PHX-0152)

- Submitted Rev 01: 13 Mar 2018; Rev 02 in progress

- R1 Apr 17: List of improvement points (PHX-0314)

- Submitted Rev 00: 13 Mar 2018; Rev 01 in progress

- M1 Jan 18: Implementation of improvement points (PHX-0316)

- Submitted Rev 00: 03 Apr 2018; Rev 01 started

- R2 Aug 19: Final Design Flow document (PHX-0152)

- Pending Final revision of PHX-0152 at the end of the project

- PDA.M2 Jun 18: Update of Smart and TU/e PDK (PHX-0639)

- Pending

## DF Improvement Points

#### M1 Implemented Improvement points

- Including Modal Properties in PDKs

- Available in OptoDesigner 5.2

- Extend documentation

- Black Box Handling (GDS + SPT)

- Available in OptoDesigner 5.2

- Adding new classes for usability

- Use case tested, initial documentation submitted, need some cleanup.

- Autorouting

- Available in OptoDesigner 5.2

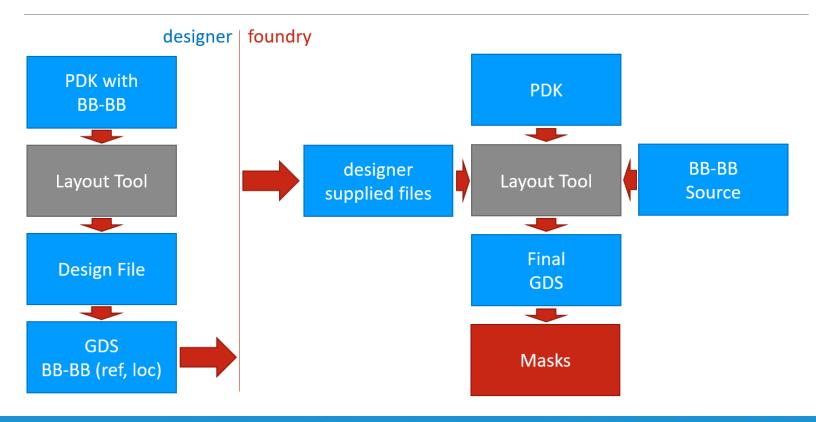

## Black Box use case

# User design

```

/* --- PDK (make sure nothing else from spt in PDAConfig.ini is used) --- */

pda::loadFoundry("NONE");

pda::enableFoundry("NONE");

/* --- Load Layout library, and SPT files marked as Layout --- */

#include @layout;

/* --- Design with a simple Black Box --- */

ml::Straight( cin -> [0, 0, 30] : wfix(1), 10);

ml::imosStraightNoParams BlackBox(last:); /* 10 X 0.4 rectangle */

ml::Straight( last : wfix(2), 10);

ml::imosGDSCellA BlackBox(last:);

ml::Straight( last : wfix(3), 10);

/* --- Export the design with Black Boxes ---*/

pdkExport("./Export/UserDesign", "GDSTopCell");

```

# User Export

```

#include @layout;

layout final GDSTopCell() {

mask::setLayoutPort(this, "org");

string fMain=mask::loadFile(DIR UserDesigns+"\UserDesign04-04-2018 IMOS.gds",true);

ml::Maskfile MapLayer(wher->this@org : fMain,,,1,);

ml::imosStraightNoParams BBSource(org->this@org+[8.66025, 5.00000, 30.00000] : 0 ) CMP3;

ml::final GDSTopCell(org->[0,0]:);

string projectname = "ProjectIMOS";

// Load GDS file

string fLib=mask::loadFile("cellLibIMOS.gds",false);

var curs0=mask::getCursor(fLib, "GDSCellA");

ml::maskCursor(wher-> [25.98076, 15.00000, 30.00000] : &curs0,1,true);

```

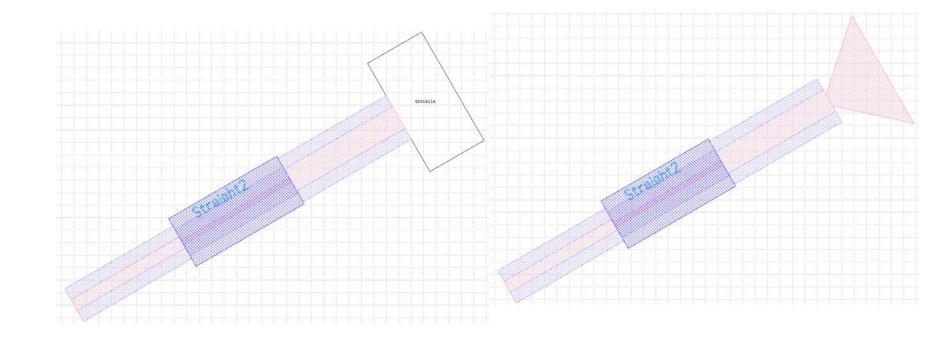

# Foundry assembly

```

string fLib=mask::loadFile("cellLibIMOS.gds",false);

var curs0=mask::getCursor(fLib,"GDSCellA");

ml::maskCursor(wher-> [

30.00000] : &curs0,1,true);

25.98076,

15.00000,

ml::imosStraightNoParams_BBSource(org->[

8.66025.

5.00000.

30.00000] : 0 ) CMP3;

Vlayout final_GDSTopCell() {

mask::setLayoutPort(this,"org");

string fMain=mask::loadFile("UserDesign15-03-2018 IMOS.gds",true);

ml::Maskfile_MapLayer(wher->this@org : fMain,,,1,);

Straight2

```

# Foundry Export

## Execution Flow WP3.4.EF

- Deliverables

- R0: Execution Flow Document (PHX-0258)

- Not submitted

- M0: Implementation of an Execution DB

- R1: Final Execution Flow Document

- Focus on how to include manufacturing process and measurements

- Need to provide measurement support files from the design tools

- Is available in OptoDesigner

- Need to know related information for analysis

### PDAFlow WP3.4.PDA

#### Deliverables

- M0 Mar 17: Development of PDAFlow template (PHX-0317)

- Submitted: 19 Jun 2017

- M1 Apr 17: Implementation of first Building Block

- Implemented: no specific document yet.

- R0 Mar 17: Full documentation of template (PHX-0112)

- Submitted: 13 Mar 2018

#### PDAFlow developments

- Set up compile environment at TU/e

- Basic IMOS PDK implemented with online documentation

- Problems with ADS implementation

# **DRC** Improvements

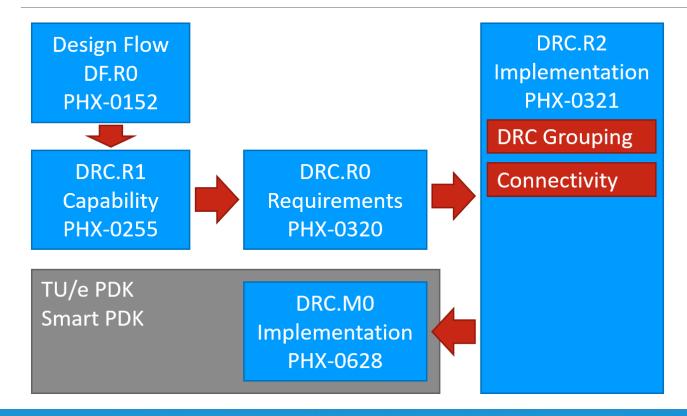

# Design Rule Checks WP3.4.DRC

#### Deliverables

- R0 May 17: DRC requirement report (PHX-0320)

- Submitted: 03 April 2018 (Improvement Points)

- R1 Aug 17: Documentation of DRC Capability (PHX-0255)

- Submitted: 14 March 2018 Rev 01

- M0 Nov 17: DRC Implementation in PDKs (PHX-0628)

- Submitted: 12 March 2018

- R2 Aug 18: Implementation of new DRC functionality (PHX-0321)

- Submitted: 03 April 2018 Rev 00

# **DRC Improvement Points**

- DRC developments

- Implemented grouping PDK capability

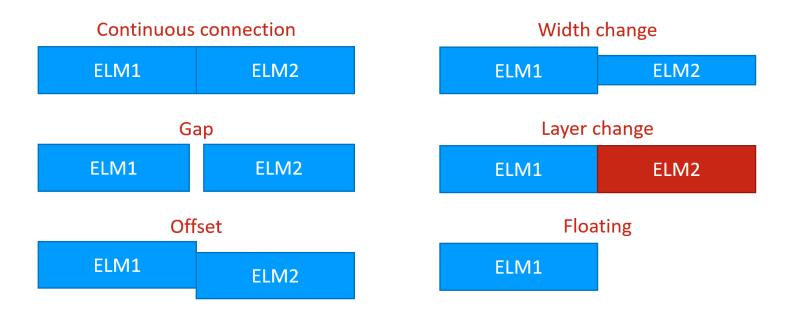

- Connectivity checks

# Connectivity

## www.phoenixbv.com

## marcel@phoenixbv.com

© COPYRIGHT 2017-2018 SYNOPSYS, INC. THIS SYNOPSYS MANUAL AND ALL ASSOCIATED DOCUMENTATION ARE PROPRIETARY TO SYNOPSYS, INC. AND MAY ONLY BE USED PURSUANT TO THE TERMS AND CONDITIONS OF A WRITTEN LICENSE AGREEMENT WITH SYNOPSYS, INC. ALL OTHER USE, REPRODUCTION, MODIFICATION, OR DISTRIBUTION OF THE SYNOPSYS MANUAL OR THE ASSOCIATED DOCUMENTATION IS STRICTLY PROHIBITED.