## **Open Innovation Photonic ICs**

# **OpenPICs**

## **Technical Summary Report**

# (09/2016 - 06/2017)

## Table of Contents

| TABLE OF CONTENTS                                                                                         | 2  |

|-----------------------------------------------------------------------------------------------------------|----|

| INTRODUCTION                                                                                              | 3  |

| WORK PACKAGE 1 - MARKET DEMANDS                                                                           | 4  |

| MILESTONE SUMMARY (WP1.M1): LINKING PRODUCTS TO BUILDING BLOCKS                                           | 5  |

| MILESTONE SUMMARY (WP1.M2): SURVEY OF REQUIREMENTS AND BUILDING BLOCKS                                    | 6  |

| MILESTONE SUMMARY (WP1.M5): TRAINING AND OUTREACH                                                         | 7  |

| WORK PACKAGE 2 – PROCESS CHARACTERISATION                                                                 | 8  |

| MILESTONE SUMMARY (WP2.M0.1): WP2 PROJECT CHARTER                                                         |    |

| MILESTONE SUMMARY (WP2.1.M1.2): GENERIC MPW PLANNING & UPDATE Q3'16 - Q2'17 DATA                          | 11 |

| MILESTONE SUMMARY (WP2.1.M1.1): LIST OF GENERIC MPW PARAMETERS FOR DATA MONITORING AND IMPROVEMENT        | 12 |

| MILESTONE SUMMARY (WP2.1.M1.2): GENERIC MPW PARAMETERS – UPDATE Q2-2017                                   | 13 |

| MILESTONE SUMMARY (WP2.1.M1.1): GENERIC BB IMPROVEMENTS – METALLIZATION LIFT-OFF                          | 14 |

| MILESTONE SUMMARY (WP2.2.M2.1): GENERIC BB IMPROVEMENTS: THRESHOLD CURRENT & PASSIVATION - DIELECTRIC     |    |

| MATERIAL QUALITY                                                                                          | 15 |

| MILESTONE SUMMARY (WP2.2.M2.2): GENERIC BB IMPROVEMENTS THRESHOLD CURRENT & PASSIVATION – INTEGRATION     |    |

| IMPROVEMENT                                                                                               | 16 |

| WORK PACKAGE 3 – BUILDING BLOCK IMPROVEMENT                                                               | 17 |

| MILESTONE SUMMARY (WP3.1.M0): TECHNOLOGY AND DESIGN CONCEPT – MODULATOR                                   | 18 |

| MILESTONE SUMMARY (WP3.1.M0): TECHNOLOGY AND DESIGN CONCEPT - RF LINES                                    | 19 |

| REPORT SUMMARY (WP3.1.RO): ANALYSIS AND DESIGN - MODULATOR                                                | 20 |

| REPORT SUMMARY (WP3.1.RO): ANALYSIS AND DESIGN – RF LINE                                                  | 21 |

| MILESTONE SUMMARY (WP3.1.M1): MASK DESIGN TAPE OUT - MODULATOR                                            | 22 |

| MILESTONE SUMMARY (WP3.1.M1): MASK DESIGN TAPE OUT – RF LINE                                              | 23 |

| MILESTONE SUMMARY (WP3.2.MO): REPORT ON THE CURRENT STATE OF THE PDK AND ISSUES LIST                      | 24 |

| MILESTONE SUMMARY (WP3.2.M1): FIGURE OF MERIT FOR THE BUILDING BLOCKS FROM MPW SMART PDK                  | 25 |

| MILESTONE SUMMARY (WP3.2.M2): DEFINITION OF COMPOSITE BB FIGURE OF MERITS                                 | 26 |

| REPORT SUMMARY (WP3.2.RO): DEFINITION OF MEASUREMENT PROCEDURES                                           | 27 |

| REPORT SUMMARY (WP3.3.RO): DESIGN OF STANDARD MPW BUILDING BLOCK TEST CELL                                |    |

| MILESTONE SUMMARY (WP3.4.PDA.MO): DEVELOPMENT OF PDAFLOW TEMPLATE                                         | 29 |

| REPORT SUMMARY (WP3.5.RO): 400G TRANSMITTER CONCEPT                                                       | 30 |

| Report Summary (WP3.5.R1): Demonstrator Sensing                                                           | 31 |

| WORK PACKAGE 4 – PROCESS IMPROVEMENT                                                                      | 32 |

| MILESTONE SUMMARY (WP4.M1.1): SPECIFIC TASKS AND MILESTONES DEFINED; WP STARTED. (WP4.M1.2): QUANTIFIABLE |    |

| CRITERIA FOR EACH MILESTONE DEFINED                                                                       | 33 |

| MILESTONE SUMMARY (WP4.M3.1): ZN-DIFFUSION TIME DETERMINED: READY FOR JOINT MPW VALIDATION                | 34 |

| MILESTONE SUMMARY (WP4-M5.1): DUV LITHOGRAPHY INTRODUCED TO MPW                                           | 35 |

| PARTNERS                                                                                                  | 36 |

## Introduction

Photonic Integrated Circuits (PICs) are key enablers for data transmission and sensing in the More than Moore paradigm. These integrated circuits process light to exploit the massive bandwidth, energy efficiency as well as phase and polarization properties of light for more precise measurements. Historically, PICs have been first applied in the telecom area as the transmitter and receiver devices that send information through optical fibre. In recent years, with the explosive growth of internet services, photonic circuits are extensively used there for information transfer and processing, enabling a reduction in power consumption and an increase in efficiency and performance. In addition, PICs are opening up new possibilities, in fields such as health care, biological imaging and the monitoring of mechanical structures. The North Brabant region is a leader in the field of photonics and is home to leading research facilities and an innovative photonics industry. With the Open Innovation Photonic IC (OpenPICs) project, participating partners strengthen this position by providing a strong industrial platform for PIC production for a new wave of PIC-enabled products.

The technology for the production of photonic circuits still needs to be optimized, both in terms of design as well as manufacturing processes. At present, several technological challenges need to be overcome to make this technology suitable for a wider uptake and to lay the foundation for capitalizing on the opportunities. The OpenPICs project addresses these issues and is organized around the following four work packages:

- 1) Market Demands

- 2) Process Characterisation

- 3) Building Block Improvement

- 4) Process Improvement

This technical report gives a summary of the major activities undertaken within the listed four work packages between September 2016 and June 2017.

## Work Package 1 - Market Demands

## Milestone Summary (WP1.M1): Linking Products to Building Blocks

## Author: Weiming Yao

#### Goals

The generic integration platform for photonic integrated circuits provides mature building blocks that can be used to construct complete systems for product development. However, this technology push approach needs to be complemented by a market pull initiative, where products are identified that have significant market impact and their specifications are then mapped to building block requirements, giving focus to R&D efforts. The goal of this activity is to relate promising products to building block definitions and metrics.

- Together with Technobis and Effect Photonics, we have identified two products as very promising with high impact market potential, namely the fiber sensor interrogator and the optical transmitter.

- We agreed on high-level specifications and system architectures of both applications so that the required subsystems in form of building blocks are defined.

- In case of the fiber sensor interrogator unit, a widely continuous tuneable laser with low linewidth is desired in combination with a high-precision filter. This requires improvement in the MZI, AWG and grating filter building blocks.

- In case of the optical transmitter, seamless integration of a tuneable laser and a high-speed modulator building block are desired. Both the laser and modulator performance need to be improved as well.

- More details are reported in the milestones WP3.5.R0 and WP3.5.R1

## Milestone Summary (WP1.M2): Survey of requirements and building blocks

## Author: Weiming Yao

#### Goals

The generic integration platform offers a wide range of basic and composite building blocks that need to undergo continued development towards higher performance and lower cost. In order to identify the most demanded building blocks and the amount of information the process design kit (PDK) should contain, we perform a technical survey with our expert partners.

#### Achievements

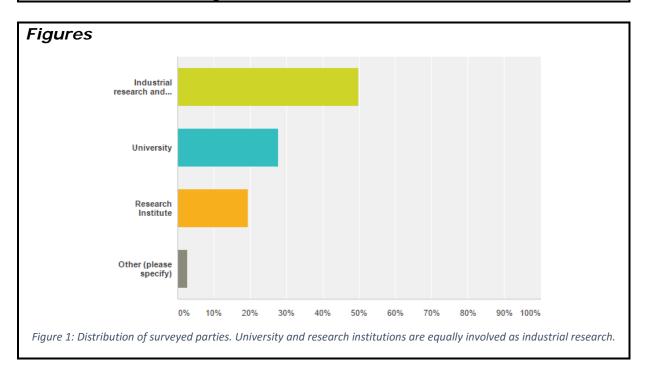

- We designed and created an extensive survey with the purpose to gather information on all available building blocks in the Smart Photonics generic platform.

- We received over 35 detailed responses from both academia and industry that give us insightful information.

- New technical insight was gained by analysing the preferred building blocks and their specifications.

- New business insight was gained through analysing the preferred cost per chip and cost for additional PDK information metrics.

- The survey acts as a valuable input for the platform roadmap in both the short and long term.

## Milestone Summary (WP1.M5): Training and Outreach Author: Aura Higuera Rodriguez

#### Goals

Reach out activities for PICs on open access InP platforms

| Achievements                                                                   |

|--------------------------------------------------------------------------------|

| <ul> <li>More than 20 entities scouted:</li> </ul>                             |

| o SMEs                                                                         |

| o Universities                                                                 |

| <ul> <li>Mid-caps , corporates and multi-nationals</li> </ul>                  |

| <ul> <li>Main topics:</li> </ul>                                               |

| <ul> <li>Data-com (tuneable sources, C and L band operation in same</li> </ul> |

| chip)                                                                          |

| o Tele-com                                                                     |

| <ul> <li>Sensing (fiber sensing, gas sensing)</li> </ul>                       |

| <ul> <li>Events participation and organization</li> </ul>                      |

| <ul> <li>PIC international 2017</li> </ul>                                     |

| <ul> <li>OFC 2017 workshop and exhibition</li> </ul>                           |

| <ul> <li>World Technology Mapping Forum</li> </ul>                             |

| <ul> <li>ECOC 2017 workshop</li> </ul>                                         |

| <ul> <li>Trainings</li> </ul>                                                  |

| <ul> <li>JePPIX training in Beijing 2016</li> </ul>                            |

| <ul> <li>JePPIX training in Eindhoven 2016</li> </ul>                          |

| <ul> <li>Joint training with 7Pennings in LA 2017</li> </ul>                   |

| <ul> <li>JePPIX training 2017 Netherlands</li> </ul>                           |

| <ul> <li>JePPIX training China 2017 (work in progress)</li> </ul>              |

| <ul> <li>Outreach to users for feedback:</li> </ul>                            |

| $\circ$ Well-developed generic platforms (more and more efficient              |

| BBB)                                                                           |

| <ul> <li>Reliability</li> </ul>                                                |

| <ul> <li>Punctuality of MPW runs</li> </ul>                                    |

| <ul> <li>Feasibility of PIC designs</li> </ul>                                 |

| <ul> <li>Deep description of modules</li> </ul>                                |

| <ul> <li>Statistics of functioning</li> </ul>                                  |

| <ul> <li>Modelling</li> </ul>                                                  |

|                                                                                |

## Work Package 2 – Process Characterisation

## Milestone Summary (WP2.M0.1): WP2 Project Charter Author: Roel Daamen, Rob Geertman

| General          |                                                                                                                        |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Project Name:    | WP2: Tracking and Process Improvement of Existing Building Blocks and Introduction of New Building blocks into the MPW |  |  |

| Project Sponsor: | Stimulus OpenPICs                                                                                                      |  |  |

| Project Manager: | Rob Geertman                                                                                                           |  |  |

#### Business Case Statement

[Why is the project being undertaken? What is the background of this project? What is the cost/benefit of the project?]

#### SMART:

Process- and PDK-improvements of Generic Building Blocks and Extension of the library with new Building Blocks is essential for the success of SMART as a foundry.

#### OpenPICs:

The project promotes process development and ensures that a technological edge is maintained through innovative building blocks, processes and products for use by end users.

Cooperation with TU/e and other members of OpenPICs. Introduce and improve processes of Generic Building Blocks to a maturity level ready for PDK introduction.

#### **Problem Statements**

- 1. Functionality of Initial BB is proven, but stability over time is not yet proven

- 2. New BB introduced on existing MPW should not interfere with existing BB quality

- 3. Current maturity level of Process flow or existing BB's is not yet high enough

#### **Goal Statement**

- 1. Improve on the stability/variation on the current set of BB's (baseline)

- 2. Reach predefined quality level, specified for new BB's, without interfering current parameters

- 3. Incorporate new BB's into the standard MPW flow (baseline update)

Open Innovation Photonic ICs - Technical Summary Report

#### **Project Scope**

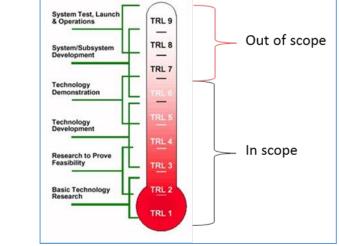

#### **Deliverables:**

- Track BB parameters in available BB's (WP2.1)

- Improve quality and variation in available BB's (WP2.2)

- Introduce new BB's in the MPW (and PDK) with predefined quality (WP2.3)

Assumptions: [What is the team assuming to be true?]

Initial BB quality is within reach of SMART's capabilities (e.g. acceptable quality products with goo d uniformity) with current and/or to-be updated tool set

**Constraints:** [What are the limiting factors such as the budget or deadlines?]

- Limited set of information due to MPW-run approach

- Old equipment set not always ideally suited to get stable performance

- Smart' organization and man power is in the build-up phase

- **Out of Scope:** [What will be excluded from this project?]

- Manufacturing Yield is out of scope (i.e. TRL7t/m9)

• MPW process is still under improvement, this could interfere with the quality of BB's

#### High-Level Project Risks

- Complex processing and design interaction could lead to less-usable BB's or at an unacceptable low performance (potentially longer development time needed for decent performance)

- Internal communication with many partners, limited project management experience. Hence, timely delivery of new BB's is ambitious

#### Stakeholders & Affected Business Areas [Who will be impacted by this project?]

• SMART as a foundry, partners at OpenPICs

#### Core Team Members

• Roel Daamen (0.7), Rob Geertman (0.1), Erik den Haan (0.1), Kostas Voutyras(0.3) (all Smart Photonics)

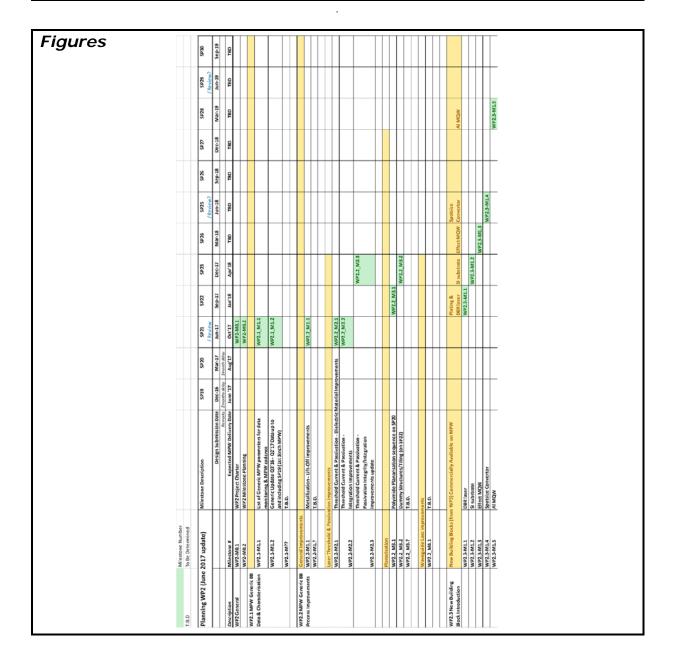

## Milestone Summary (WP2.1.M1.2): Generic MPW Planning & Update Q3'16 - Q2'17 Data Author: Roel Daamen

#### Goals

Show initial WP2 Milestone planning and related MPW cycle.

#### Achievements

• Initial WP2 Milestone Planning & MPW cycle available.

# Milestone Summary (WP2.1.M1.1): List of Generic MPW parameters for data monitoring and improvement

## Author: Roel Daamen

#### Goals

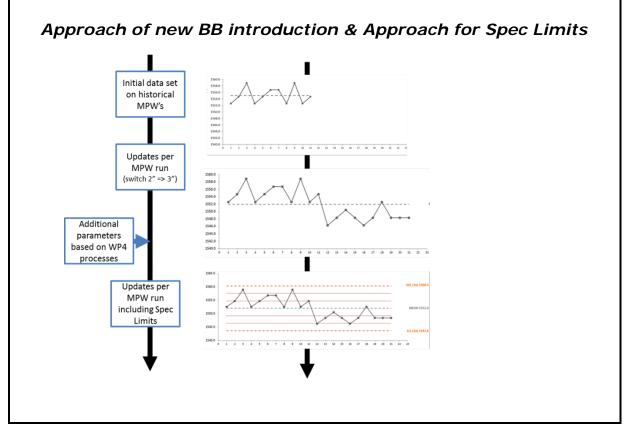

Define the initial list of Process/Performance Parameters that will be tracked to improve the MPW's as part of OpenPICS.

Schematically describe the approach to get to a better controlled MPW performance

#### Achievements

- Initial list of Parameters has been selected

Will be populated with more items during the course of the project

- Schematic approach of New BB introduction

#### MPW & BB parameters

- 1) Epitaxy

- 2) Waveguide Processing

- 3) Building Block Performance

- 4) Extend data set with New BB's (from WP3)

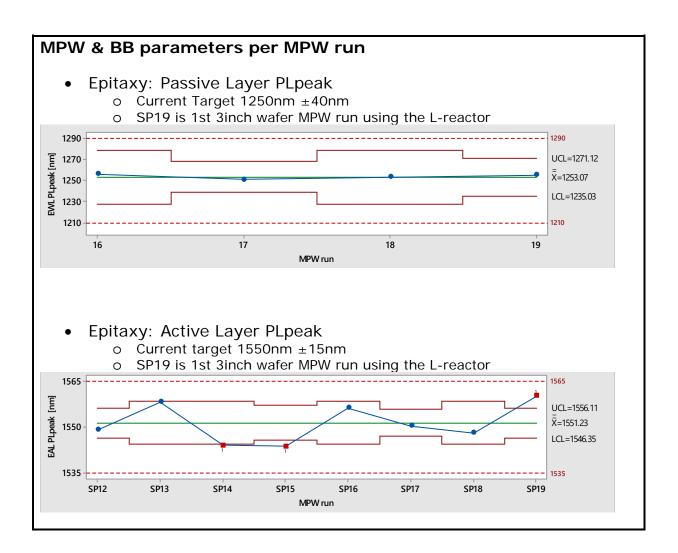

## Milestone Summary (WP2.1.M1.2): Generic MPW Parameters – Update Q2-2017

### Author: Roel Daamen

#### Goals

Track the MPW performance indicators over time to improve process stability

#### Achievements

- Generated historical MPW data available for few selected items from Epitaxy (Active PLpeak, Passive PLpeak), Processing (Shallow Waveguide Width and BB performance (Waveguide Loss and Laser Threshold Current)

- Will be populated with more items and limits during the course of the OPENPICS project

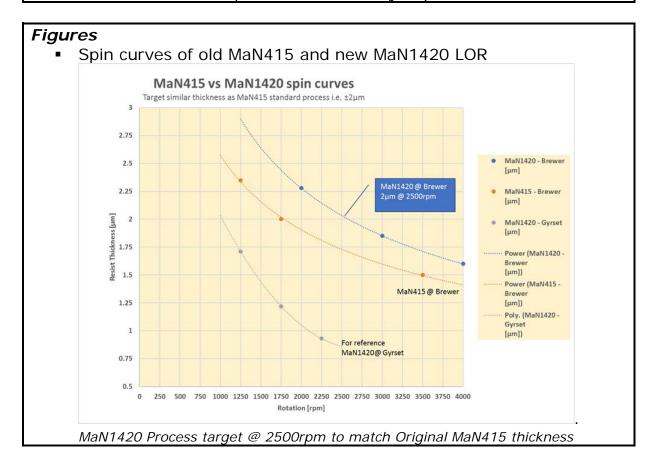

## Milestone Summary (WP2.1.M1.1): Generic BB Improvements – Metallization Lift-off

## Author: Roel Daamen

#### Goals

Reduce Metal Residues remaining after the Lift-Off process & Improve Narrow Line CD performance. Process should be applicable for Metals deposited by Evaporation & Sputter deposition

#### Achievements

- A process assessment was carried out on the existing Lift-Off Resist (LOR) process (i.e. MaN415)

- A new LOR with better Thermal Properties (higher Tg) was selected (MaN1420)

- The new LOR was successfully applied on InP wafers with Full Topography resulting in a new and improved Lift-Off process with reduced metal residues

- Critical Dimension (CD) performance of the MaN1420 at targeted line widths of 2.5 and 5µm has dramatically improved

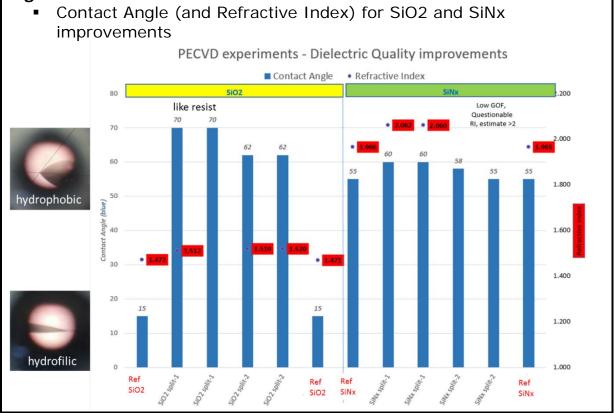

## Milestone Summary (WP2.2.M2.1): Generic BB Improvements: Threshold Current & Passivation -Dielectric Material Quality Author: Roel Daamen

#### Goals

Current dielectric materials SiO2 and SiNX are of relatively poor quality, especially SiO2 has high leakage and is prone to absorb moisture. Goal is to obtain higher Quality SiO2 (and SiNx) dielectric materials to be used for an Updated/Upgraded Passivation.

#### Achievements

- Contact Angle of SiO2 has been improved form a hydrophilic 15° to a hydrophobic contact angle >60°, small SiNx improvements. Contact angle stays stable over time

- Dielectric Breakdown improvements in SiO2 Split-1 removing all early fails around 85V with consistent breakdown occurring >160V

- Dielectric Breakdown improvements in SiNx Split-2 improving

#### Figures

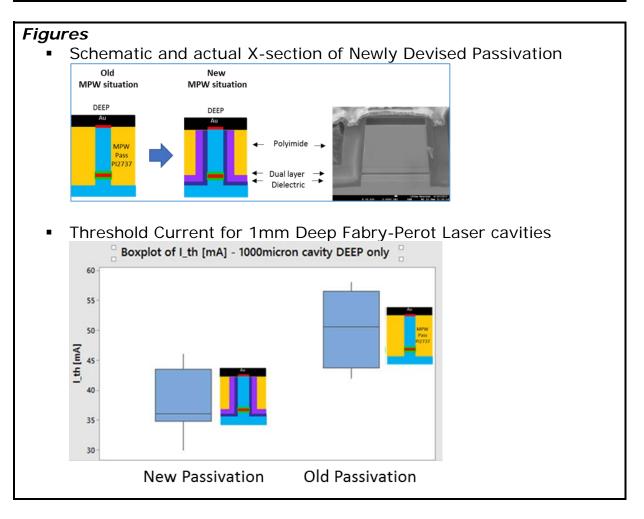

## Milestone Summary (WP2.2.M2.2): Generic BB Improvements Threshold Current & Passivation – Integration Improvement Author: Roel Daamen

#### Goals

Improve the current MPW passivation to improve generic reliability (a.o. for lasers)

- New Passivation Integration approach identified and after several developments implemented on test wafers using Higher Quality Dielectrics (see WP2.2-M2.1)

- Dry etch recipes updated to better match existing Etch rates

- Excellent Laser Threshold currents were obtained in the deep sections where the Passivation is key.

- Excellent Reliability results obtained for the New Passivation

- New Passivation approach implemented on MPW SP19

## Work Package 3 – Building Block Improvement

## Milestone Summary (WP3.1.M0): Technology and Design Concept – Modulator

## Author: Weiming Yao

#### Goals

The goal is to outline concepts that will be pursuit for the high-speed modulator building block within this project and to indicate requirements on the technology platform.

#### Achievements

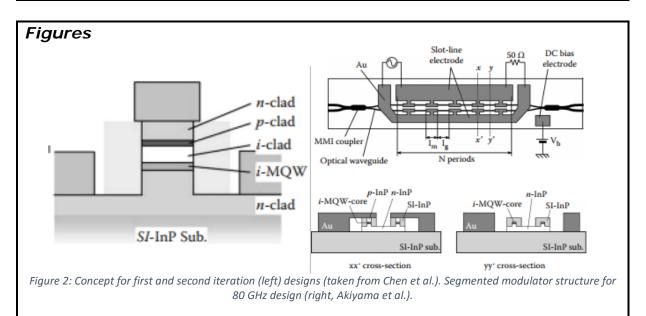

- We are planning to follow an iterative design approach for the modulator building block with 28, 56 and 112 Gbaud as target symbol rates.

- Relevant specifications are listed and given for the modulator BB to reach competitive performances.

- Based on literature study, speed limiting factors and design variants for high-speed modulators are presented and the CPW and segmented modulator electrode are chosen for this project to achieve the targeted performance.

- Initial requirements on the platform and in particular requirements on lithographic resolution are discussed. It can be concluded that the electrode geometry can be realized within the existing platform capabilities.

- The platform will need to transition to quantum well material and semi-insulating substrate in order to reach the targeted performance values.

## Milestone Summary (WP3.1.M0): Technology and Design Concept - RF Lines Author: Weiming Yao

#### Goals

The goal is to finalize the concept that will be pursuit for the high-speed RF line building block within this project and to indicate requirements on the technology platform.

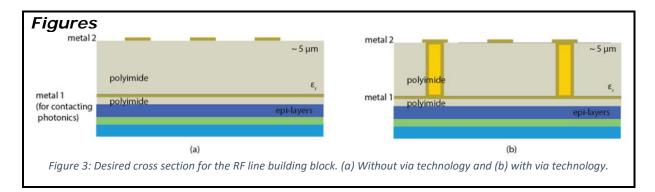

- We decided to follow an iterative development procedure for the RF lines with incremental bandwidth increases from 20 GHz to 40 GHz and 80 GHz. Specifications on attenuation, length, impedance and return loss have been finalized.

- We investigated main factors that influence RF bandwidth and explored how these can be minimized through literature research and simulations. This led to the proposal of a novel RF line concept that is compatible to the generic platform.

- First details of the new concept have been established and its requirements on the platform technology have been discussed.

- The concept is illustrated in Fig. 1. A second level passivation layer using either polyimide or BCB acts as the dielectric material for the RF line building block. Via technology will be developed to connect the second level metal to the first level metal.

- This ensures low-loss transmission lines and adequate spatial separation of the RF field from the photonic layer.

## Report Summary (WP3.1.R0): Analysis and Design -Modulator

## Author: Weiming Yao

#### Goals

This report details the analysis and design of the first iteration high-speed modulator, which has been taped-out in current multi-project fabrication runs for validation.

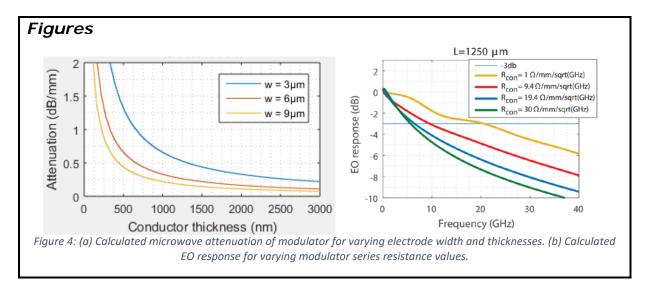

- We detailed and motivated the need for incorporating multi quantum-well (MQW) material in the modulators in order to reduce drive voltage and therefore power consumption.

- MQW material growth and implementation in MPW runs is performed by Smart Photonics in close collaboration with Effect Photonics

- We analysed the influence of electro-plated metal on the modulator speed and performance. Skin-effect and resistive losses can be significantly reduced, motivating the use of thicker metal electrodes (Fig. 1).

- This is implemented since SP19 and its performance will be studied on modulators of SP20.

- Influence factors on modulator speed are analysed on the basis of a coplanar waveguide electrode configuration.

- Useful dimensions for the first iteration modulator design are synthesized for mask layout.

### Report Summary (WP3.1.R0): Analysis and Design – RF Line

## Author: Weiming Yao

#### Goals

This report details the analysis and design of the first iteration broadband RF line component for routing high-speed signals on the photonic circuit.

- We analysed the drawbacks of the existing RF line component design and indicated the main factors for achieving broadband operation. Major loss sources are doped p- and n- semiconductor layers that are neither ideal conductors nor dielectrics.

- Based on the insight, we propose a two-layer concept that overcomes the existing loss limitations through the insertion of a dielectric layer on top of the photonic circuit. Metal routing will be introduced on top of the latter dielectric layer.

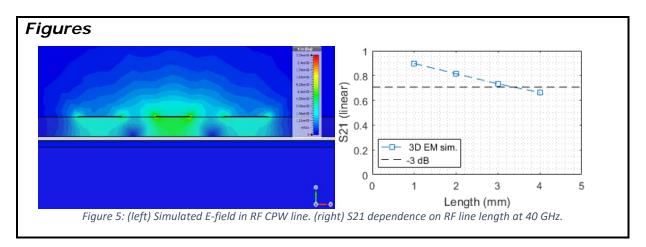

- 3D electro-magnetic simulations are performed that confirm the broadband operation of the proposed RF line structure.

- The design is made compatible to the existing generic platform.

- Shielding planes are proposed that further promotes the separation of RF and optical functionality to guarantee low loss operation of both.

- Estimation of the bandwidth of the new structure yields >80 Ghz operation if length < 3 mm.</li>

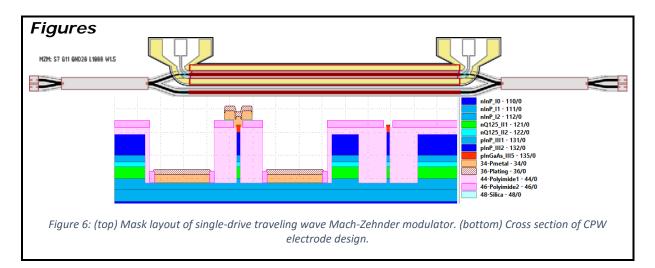

## Milestone Summary (WP3.1.M1): Mask Design Tape Out - Modulator

## Author: Weiming Yao

#### Goals

The results from the analysis and design of the first iteration modulator building block are used to create the mask layout for the first design tape out.

- We designed a range of modulator devices with varying geometric parameters around simulated optimum values and implemented them into mask layout.

- The designs were made to support high-speed on-chip probing for accurate device characterisation and testing.

- A new n-side contact and grounding scheme with n-metallization is accounted for.

- A test cell was filled with arrays of modulators, similar as shown in Fig. 1, so that both the electro-optic efficiency and EO bandwidth can be tested.

- In addition, microwave transmission line test structures have been designed that explore in more variation the electrode design space for the modulator component.

- The test cell has been released to SP20 which is based on a semiinsulating InP substrate and will be repeated in SP21 which in addition incorporates MQW material for lowering the drive voltage.

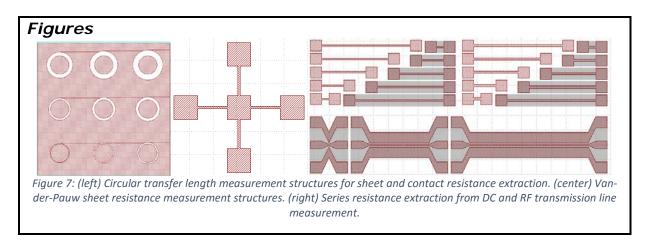

## Milestone Summary (WP3.1.M1): Mask Design Tape Out – RF Line

## Author: Weiming Yao

#### Goals

Test structures are to be designed that give more information on RF related material parameters of the platform in order to feed back into the highspeed component design.

- We designed and implemented test structures for RF parameter extraction into run SP19. The designs will be repeated in subsequent MPW runs to track the evolution of RF parameters.

- Knowledge of material sheet and contact resistance to metal is important for RF line and modulator development. The circular transfer length test structure is very suitable to extract both and has been implemented in mask layout (Fig. 1 left) for varying underlying layer compositions.

- The metal series resistance is an important parameter that determines RF loss and can be extracted from Van Der Pauw measurements on structures shown in Fig. 1 center.

- The series resistance at DC and high frequencies can be measured from the structures shown in Fig. 1 right. RF transmission lines can be characterized and the obtained S-Parameters can be used to fit a general RLGC model in order to determine the R component.

# Milestone Summary (WP3.2.M0): Report on the current state of the PDK and issues list

#### Authors: Rui Santos

#### Goals

This report describes the status of the SMART Photonics MPW PDK. This includes an overview of the design manual, building blocks and design rules is made.

#### Achievements

- Description of the state of the art of the SMART Photonics PDK

- Description of the improvements to be added to the PDK

- o Extended version of the DRC.

- o Experimental data of BB.

- Inclusion of new BB to the PDK.

#### **Current status of the SMART Photonics PDK**

A Process Design Kit (PDK) is a collection of foundry-specific data files and script files used in a specific chip design flow. A PDK's main components are models, symbols, technology files, parameterized cells, and rule files. The PDK is mostly, but not entirely, described in the design manual from the foundry.

Currently the SMART Photonics MPW PDK is described in the design manual version 0.3 released November 4<sup>th</sup> 2016 (**Error! Reference source not found.**). The PDK is now implemented in the mask layout software PhoeniX OptoDesigner.

**SMART**Photonics

SMART Photonics Photonic IC design manual Version V 3.3 November 4. 2016 SMART Photonics in collaboration with Photonic Integration group COBBA research center Eindhoven University of Technology

CONFIDENTIAL

Figure 8: SMART Photonics manual.

## Milestone Summary (WP3.2.M1): Figure of Merit for the building blocks from MPW SMART PDK

## Authors: Rui Santos

#### Goals

This report identifies the figures of merit (FoM) of all the building blocks available in the SMART Photonics MPW PDK. The objective is to identify the key parameters that will enable setting performance specifications.

#### Achievements

Definition of the FoM of the building blocks.

#### Figure of Merit for the Building Blocks

The Figure of Merit (FoM) is the identification of the main performance characteristic that will be used for validation of the performance of each individual building block (BB). In the following table a list of the BB with the corresponding FoM, including the measurements units, is shown.

| Туре    | Name                           | FoM                   | units                         |

|---------|--------------------------------|-----------------------|-------------------------------|

| *       | <b>•</b>                       | <b>•</b>              | <b>•</b>                      |

| oassive | Shallow waveguide              | waveguide loss        | dB/cm                         |

| oassive | Deep Waveguides                | waveguide loss        | dB/cm                         |

| oassive | Shallow curve                  | excess loss           | dB/90°                        |

| passive | Deep curve                     | excess loss           | dB/90°                        |

| passive | Linear Taper                   | insertion loss        | dB                            |

| passive | Parabolic Taper                | insertion loss        | dB                            |

| passive | MMI coupler 1x1                | insertion loss        | dB                            |

| passive | MMI coupler 1x2 Shallow        | split ratio           | dB                            |

| oassive | MMI coupler 1x2 Deep           | split ratio           | dB                            |

| passive | MMI coupler 1x2 Low Reflec     | split ratio           | dB                            |

| passive | MMI coupler 2x2 Shallow        | split ratio           | dB                            |

| passive | MMI coupler 2x2 Deep           | split ratio           | dB                            |

| passive | MMI coupler 2x2 8515 Shallow   | split ratio           | dB                            |

| passive | MMI coupler 2x2 8515 Deep      | split ratio           | dB                            |

| passive | MMI coupler 2x2 7228 Shallow   | split ratio           | dB                            |

| passive | MMI coupler 2x2 7228 Deep      | split ratio           | dB                            |

| oassive | Shallow Deep transition        | insertion loss        | dB                            |

| oassive | waveguide crossing shallow     | insertion loss        | dB                            |

| passive | waveguide crossing deep        | insertion loss        | dB                            |

| passive | isolation section shallow      | electrical resistance | Ω                             |

| oassive | isolation section deep         | electrical resistance | Ω                             |

| active  | Phase Modulator (EOPM) shallow | EO efficiency         | °/V.mm                        |

| active  | Phase Modulator (EOPM) deep    | EO efficiency         | °/V.mm                        |

| active  | Phase Modulator (EOPM) RF      | EO efficiency         | °/V.mm                        |

| active  | SOA                            | gain@current density  | dB/cm(nm) @kA/cm <sup>2</sup> |

| active  | PIN diode                      | responsivity          | A/W                           |

| active  | Saturable absorber             | absorption            | A/W                           |

| oassive | DBR                            | wavelength            | nm                            |

#### SMART PHOTONICS Building Blocks

## Milestone Summary (WP3.2.M2): Definition of Composite BB Figure of Merits

## Author: Weiming Yao

#### Goals

To improve on the PDK and design manual, not only basic building blocks (BBBs) but also more complex, composite building blocks (CBBs) need to be well characterized. We define here the most relevant figure of merits for the existing CBBs.

#### Achievements

- We consolidated the collection of composite building blocks from recent R&D developments on the generic integration platform.

- We defined the basic figure of merits (FoM) for the developed composite building blocks, listed below:

- o Coupled-cavity tuneable laser

- Coupled-cavity tuneable laser extended tuning range

- o Widely tuneable laser with MZI filter

- EAM modulator

- o MZM modulator

- o Mode locked ring laser

- Mode locked linear laser

- o DBR laser

- Initial concepts for extracting these FoMs have been drafted and can be implemented in future CBB test cells.

- This contributes to standardization and tracking of the composite building blocks.

Figure 9: (Top) Microphotograph of coupled-cavity laser and (bottom) picture of Mach-Zehnder modulator.

## Report Summary (WP3.2.R0): Definition of Measurement Procedures

## Author: Weiming Yao

#### Goals

Test structures have been designed to extract the figure of merits of each basic building blocks on the platform. For each test structure, this item defines the specific measurement procedures that needs to be performed in an automated manner.

- Based on previous expertise we defined electrical test structures for extracting figure or merits (FoM) for the basic building blocks (BBBs) of the platform. These test structures can be probed electrically and therefore support on-wafer automated measurements (Test Cell 2).

- Fiber alignment is still needed for the majority of pure optical FoMs such as reflection or transmission values of passive components and its measurement procedure has been specified in detail (Test Cell 1).

- A quasi-standard description is being developed for specifying the measurement procedure incorporating the source and sense conditions and pin positions of the test cell.

| ۲est Cell 1 ٦                          | Test Cell 2                        |  |

|----------------------------------------|------------------------------------|--|

| Insertion Loss EOPM                    | Spectral gain structure            |  |

| Insertion Loss Metal on top of WG      | SOA gain, saturation structure     |  |

| MMI insertion loss                     | EOPM efficiency                    |  |

| MMI reflections                        | Current injection phase efficiency |  |

| MIR reflections                        | MMI imbalance, electrical + optica |  |

| WG crossing reflection                 | Ring resonator loss measurement    |  |

| Shallow-Deep transition reflections    | PIN PD responsivity                |  |

| Shallow-Deep transition insertion loss | CD SEM for WG opening              |  |

| Isolation section insertion loss       |                                    |  |

| WG cross insertion loss                |                                    |  |

| MMI imbalance                          |                                    |  |

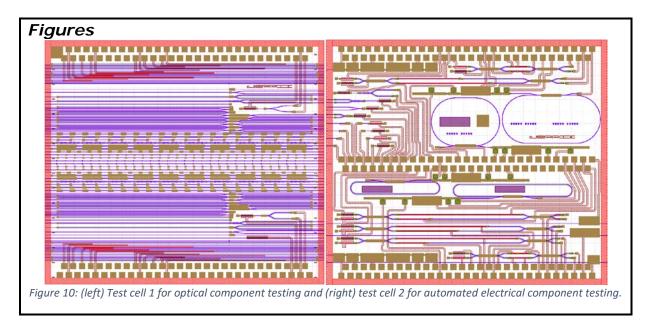

## Report Summary (WP3.3.R0): Design of Standard MPW Building Block Test Cell Author: Weiming Yao

#### Goals

Standard building blocks need improved characterization of their figure of merits, yielding values that will be tracked along different fabrication runs. This characterization should be performed in an automated way on wafer and on die from building block test cells. This item describes the design of those test cells for automated measurements.

- We created test structures for all basic building blocks offered in the platform and taped them out into two test cells (Fig. 1).

- Test cell 1 is aimed at optical component characterization, mainly for passive devices. In particular, splitting ratio, insertion loss and back reflection levels are to be measured through Fabry-Perot and OFDR measurement techniques.

- Active and EO-components are placed on cell design 2 for on-wafer and on-die automated measurements involving probe cards.

- The electrical pad layout follows quasi-standards from the running European PixApp project, tackling generic packaging solutions. This enables efficient and fast measurement of the main device parameters in the electrical domain without accessing the optical signals and enables on-wafer measurements.

- Test cells are prepared for top side n-contact as well.

## Milestone Summary (WP3.4.PDA.M0): Development of PDAFlow Template

## Authors: Marcel van der Vliet

#### Revisions

Version 0, 19 Jun 2017, Marcel van der Vliet, Initial document

## Introduction

This document discusses the status of the PDAFlow template

## PDAFlow Template

The PDAFlow template is created and documented in 'PHX-0112 PDAFlow PDAFoundry Manual.pdf' dated 9 February 2017. This document describes the procedure to add building blocks to an PDAFlow compliant PDK.

Chapter 11: 'Combining the pieces' Explains how you can start from scratch creating your own PDK. This chapter is supported with a number of spt and cc files that provide a template. This should be sufficient information to start adding Building Blocks to an existing PDK.

## Conclusions

The first draft of an PDAFlow Template is supplied, and this should enable the TU/e to start adding building blocks to PDKs.

| 🖌 foundryTemplate.cc                     | 15-6-2017 15:41 | CC File  | 3 KB |

|------------------------------------------|-----------------|----------|------|

| Yphx_foundryTemplate_views.cc            | 15-6-2017 15:41 | CC File  | 6 KB |

| / phx_template_spt.cc                    | 15-6-2017 15:41 | CC File  | 4 KB |

| template_library_02_MaskCrossSection.spt | 15-6-2017 15:41 | SPT File | 2 KB |

| 🖁 template_library_04_MaskLayout.spt     | 15-6-2017 15:41 | SPT File | 2 KB |

## Report Summary (WP3.5.R0): 400G transmitter concept Author: Saeed Tahvili

#### Goals

The goal is to propose 400G transmitter concept as the project demonstrator. Two essential building blocks which are going to be developed in this project are integrated tunable lasers and fast modulators.

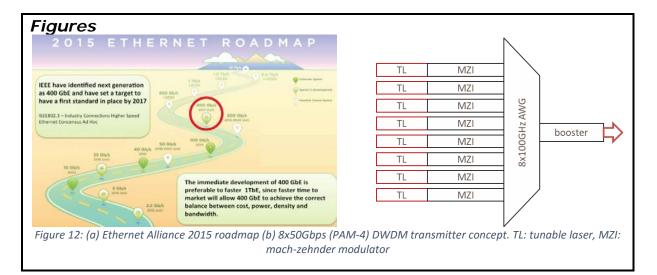

- IEEE has identified the next generation standard as 400 Gb Ethernet (400 GbE) (Figure 1.a). We decided to set a concept 400G transmitter as the project demonstrator.

- We investigated several possibilities depending on the number of (integrated) optical lanes and line rates, i.e. 16λx25Gbps, 8λx50Gbps, and 4λx100Gbps. The 8λx50Gbps option (Figure 1.b) is the most interesting option in terms of level of integration and line rate.

- Two flavours of the proposed 400G transmitter are 8  $\lambda$  lanes integrated with either 25GBaud modulators under PAM-4 modulation, or 50G bandwidth optical modulators.

## Report Summary (WP3.5.R1): Demonstrator Sensing Authors: Michael Haverdings

#### Goals

The goal is to propose a chip architecture specifically for a sensing application based on an existing product line.

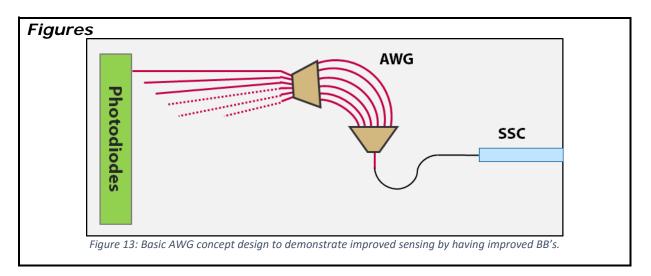

- The optical power budget relates directly to a performance improvement

- Polarization behaviour in AWG contributes to the stability of the sensing measurement. Not only in the main transmission peaks, but also in the side-lobe behaviour. On chip-polarization crosstalk is considered as a realistic source of instability. In addition, fabrication tolerances lead to polarization dependent behaviour.

- Improving the building blocks will increase the current sensing performance, setting aside potential architecture improvements. To demonstrate the performance improvement, we propose a basic AWG design with SSC.

- AWG target: side-lobe suppression at least 25 dB in wavelength range of 1500-1600 nm. IL of max -3 dB. Number of channels at least 48. Channel spacing of 200 GHz or lower (up to 50 GHz). Polarization dispersion of less than 1 pm on central channel wavelength.

- SSC target: IL of max -2 dB from fibre to chip, over a wavelength range of 1500-1600 nm. Polarization dependency of less than 0.5 dB

## Work Package 4 – Process Improvement

## Milestone Summary (WP4.M1.1): Specific tasks and milestones defined; WP started. (WP4.M1.2): Quantifiable criteria for each milestone defined Author: Longfei Shen

#### Goals

The goal is to obtain an overall planning for this work package at the starting phase of the project. The planning should be made by means of a milestone list with quantifiable criteria which can be used for reviewing the progress of this project in a later stage.

- We have planned to start with five parallel tasks in this work package, and each of them has been arranged with a task lead.

- Each task contains three milestone points and one final report. Attention has been paid to the synchronization between these milestones and the MPW run schedule that is defined in WP 2.

- Quantifiable criteria has been made for each milestone point. They are defined according to the specifications of building blocks and device demonstrators (outputs from WP 3).

- The samples and characterization methods are also proposed to for the experimental verification of these criteria.

| Tasks                                                           | Milestor | nes / <b>D</b> eliverables                                               | Responsible | Due date |

|-----------------------------------------------------------------|----------|--------------------------------------------------------------------------|-------------|----------|

| T 1. General<br>planning                                        | M 1.1    | Specific tasks and milestones defined; WP started                        | Longfei     | Dec-16   |

|                                                                 | M 1.2    | Quantifiable criteria for each milestone defined                         | Longfei     | Mar-1    |

| <u>T 2. Al-MQW</u><br><u>based</u><br>modulators                | M 2.1    | Designed MQW characterized, shallow-etch modulators demonstrated         | Longfei     | Dec-1    |

|                                                                 | M 2.2    | Etching and passivation processes developed: ready for MPW validation    | Longfei     | Jun-1    |

|                                                                 | M 2.3    | Modulator validated in MPW: ready for release                            | Rob         | Mar-1    |

|                                                                 | D 2.4    | Report on process optimization and insights for 100 Gbps modulators      | Longfei     | Jun-1    |

| <u>T 3. Zn-diffusion</u><br>based A/P<br>integration            | M 3.1    | Zn-diffusion time determined: ready for joint MPW validation             | Rene        | Jun-1    |

|                                                                 | M 3.2    | Zn-diffusion process validated in joint MPW: ready for transfer to Smart | Rene        | Mar-1    |

|                                                                 | M 3.3    | Zn-diffusion process transferred and validated in MPW: ready for release | Rob         | Dec-1    |

|                                                                 | D 3.4    | Report on process integration and device characterization                | Longfei     | Dec-1    |

| <u>T 4. Thick</u><br>insulation and<br><u>RF lines</u>          | M 4.1    | BCB insulation and metal plating tested: ready for joint MPW validation  | Tjibbe      | Sep-1    |

|                                                                 | M 4.2    | Process validated in joint MPW (post-processing): ready for transfer     | Tjibbe      | Mar-1    |

|                                                                 | M 4.3    | Process transferred and validated in MPW: ready for release              | Rob         | Sep-1    |

|                                                                 | D 4.4    | Report on process integration, insights for 100 Gbps RF lines            | Longfei     | Dec-1    |

| T 5. DUV<br>lithography and                                     | M 5.1    | DUV lithography introduced to MPW                                        | Rob         | Jun-1    |

|                                                                 | M 5.2    | Etching process optimized, ready for transfer to MPW                     | Longfei     | Mar-1    |

| etching                                                         | M 5.3    | DUV lithography introduced to Triplex platform                           | Joost       | Jan-1    |

| optimization                                                    | D 5.4    | Report on process integration (lithography and etching) in MPW           | Rob         | Jan-1    |

| <u>T 6. Stepper</u><br><u>lithography</u><br><u>integration</u> | M 6.1    | Process developed for AZ and MaN based lithography                       | Robert      | Aug-1    |

|                                                                 | M 6.2    | Overlay tested and optimized                                             | Robert      | Jan-1    |

|                                                                 | M 6.3    | Process introduced to Smart MPW                                          | Rob         | Sep-1    |

|                                                                 | D 6.4    | Report on process integration, insights for fabricating new BBs          | Longfei     | Dec-1    |

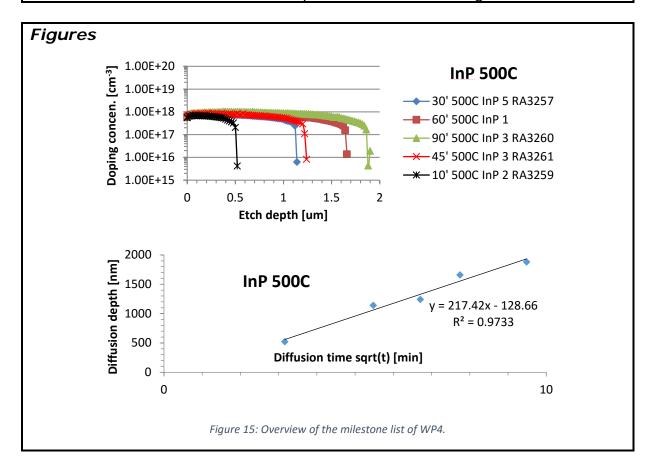

## Milestone Summary (WP4.M3.1): Zn-diffusion time determined: ready for joint MPW validation Author: Longfei Shen, Rene van Veldhoven

#### Goals

The goal is to perform Zn diffusion in epitaxial layers and characterize the diffusion rate at different conditions. The results will be used in the design of experiments with MPW wafers and processes.

#### Achievements

- We have performed successfully the Zn diffusion in a new reactor and measured the doping concentration.

- The diffusion profiles in various materials are measured at different temperatures. The diffusion rate coefficients are determined from these profiles.

- The surface quality of Zn-diffused samples covered by a SiNx mask layer has been inspected, to select the optimal process conditions.

- Zn-diffusion in MPW wafers have also been observed. A more accurate empirical model at the selected process conditions will be determined with more data points in the next stage of this task.

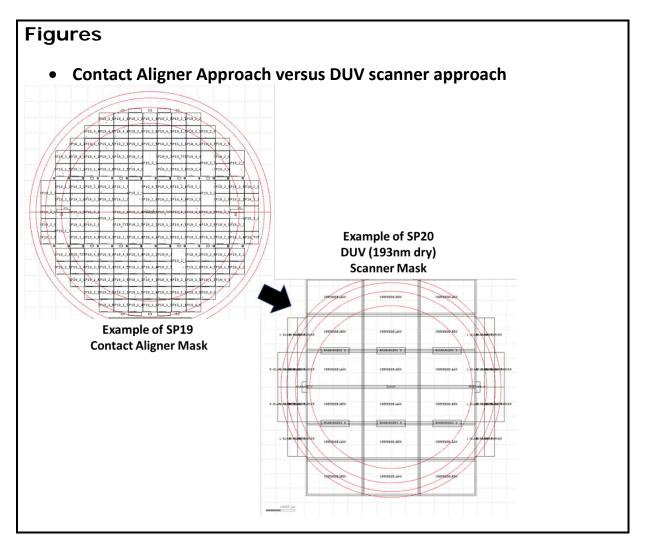

## Milestone Summary (WP4-M5.1): DUV lithography introduced to MPW

## Author: Roel Daamen, Erik den Haan

#### Goals

Introduce DUV (193nm dry) lithography in the MPW flow, starting from the SP20 run of June 2017

- For the DUV approach so-called super cells have been created, which fit 12 MPW cells of 4x4.6mm. A single supercell can be replicated 18 times on a 3 inch wafer.

- DUV mask design approach implemented on SP20, containing 2 supercells each with 9-fold replication.

## Partners

e Technische Universiteit Eindhoven University of Technology

Where innovation starts

Lion C

### Open Innovation Photonic ICs OpenPICs Technical Summary Brief (07/2017 – 12/2017)

### Photonic Integration Technology Centre

#### **Table of Contents**

| BLE OF CONTENTS1                                                                       |                                                          |

|----------------------------------------------------------------------------------------|----------------------------------------------------------|

| TRODUCTION2                                                                            |                                                          |

| ORK PACKAGE 1 – MARKET DEMANDS2                                                        | (ET DEMANDS                                              |

| Milestone (WP1.M4): Key Performance Indicators for MPW runs (KPIs)                     | : Key Performance Indicators for MPW runs (KPIs)         |

| ORK PACKAGE 2 – PROCESS CHARACTERISATION                                               | ESS CHARACTERISATION                                     |

| Milestone Summary (WP2.2-M3.1): Generic BB Improvements Planarisation Sequence on SP20 |                                                          |

| ORK PACKAGE 3 – BUILDING BLOCK IMPROVEMENT3                                            | DING BLOCK IMPROVEMENT3                                  |

| Report Summary (WP3.3.R1): Design of Composite BB Test Cell                            | P3.4.PDA.R0): Full Documentation of PDAFlow Template     |

| ORK PACKAGE 4 – PROCESS IMPROVEMENT4                                                   | ESS IMPROVEMENT4                                         |

| Milestone (WP4.M5.1): AZ resist process development on PAS 2500/40 stepper             | 1): AZ resist process development on PAS 2500/40 stepper |

| JTLOOK5                                                                                | 5                                                        |

| RTNERS5                                                                                | 5                                                        |

| Confidential, only for members of the consortium CO                                    | Confidential, only for members of the consortium CO      |

#### Introduction

The Open Innovation Photonic IC project (OpenPICs) has the goal to improve and mature photonic integration technology and widen its adoption by focusing work on four different domains: market demands, process characterization, building block improvement and process improvement. Significant work has been performed during the first reporting period (09-2016-06/2017) where the focus lied on initiating the project and establishing concepts and fundamentals in all four domains. In this reporting period, we have carried on the work along the main established lines, leading to incremental results in each domain. The following technical brief will shortly report the main achievements of this reporting period.

#### Work Package 1 – Market Demands

#### Milestone (WP1.M4): Key Performance Indicators for MPW runs (KPIs)

#### Summary

Open access technology platforms exist as a solution for PIC prototyping on a fab-less lab-less model. They provide cheap fabrication entry costs and relatively simple chip design process for first entry designers. They target public and private sector for SMEs and big companies. The ecosystem surrounding open access technology platforms include research, design, software tools and foundries. Foundries are a critical module within the ecosystem since they develop the technology for the platforms to fabricate the chips. Therefore, the MPW runs need to comply with several KPIs in order to be competitive as a PIC entry fabrication service. Those KPIs have been described. KPIs from service point of view:

- Number of leads resulting in a MPW run

- Designs per MPW run vs available cells and cumulative per year

- Price per mm<sup>2</sup> / wafer size

- Delivery time

KPIs from the technical point of view:

- Components performance per foundry

- Testing cells

- Packaging templates available

- Software tools available

#### Work Package 2 – Process Characterisation

# Milestone Summary (WP2.2-M3.1): Generic BB Improvements Planarisation Sequence on SP20

#### Goals

Improve robustness by changing/switching the Polyimide Sequence to ensure a smoother step for the Metallization (especially taking into account Semi-Insulating substrate offerings).

#### Achievements

The Polyimide order has been switched *from:* SP19: PI1 $\rightarrow$ PI2 to SP20: PI2 *Contact* $\rightarrow$ PI1 *Planarisation.*

Basic 1mm All Active laser parameters on MPW SP20A are equal to or better than SP19. SP20A Threshold Current 22.8mA/mm, Series Resistance ±3 Ohm and Slope Efficiency of 14.5%

### Milestone Summary (WP2.3.-M1.1): NEW Building Block Introduction DBR laser *Goals*

Goals

Introduce a DBR laser Building Block in the MPW flow.

#### Achievements

A tunable DBR laser with excellent performance has been implemented in SP19

- Threshold Current ±20mA

- High Output Power up to ±11mW

- Single Mode operation with SMSR > 50dB

DBR quality is good enough for creation of a Building Block and implementation into the PDK.

#### Work Package 3 – Building Block Improvement

#### Report Summary (WP3.3.R1): Design of Composite BB Test Cell

#### Goals

We designed a test cell containing the most recently developed composite building blocks to quantify and extract the most common characteristics.

#### Achievements

- We collected the recently developed cBBs including a widely tunable laser, a compact coupled-cavity laser, a Mach-Zehnder modulator, a DBR laser and an electro-absorption modulator.

- We standardized their dimensions and parameters so that the same building blocks can be used in a custom component library.

- The test cell is compatible with the standard testing pad layout to support automated measurements.

### Report Summary (WP3.4.PDA.R0): Full Documentation of PDAFlow Template

#### Summary

A complete documentation in form of a 13 chapter long document has been created that holds the necessary code examples to work with PDAFlow. The document describes in detail how PDKs can be created and building blocks can be added to the PDAFlow environment. It ends Confidential, only for members of the consortium 3 | P a g e

with aspects on how to connect the different code pieces and how a working example can be compiled. It also describes how the interface to the foundry looks like and which design aspects during coding needs to be considered.

The document is available to the members of the PDAFlow foundation, that targets to work towards a combined photonic design solution.

#### Milestone Summary (WP3.4.DRC.M0): DRC Implementation in PDKs

#### Summary

A DRC deck is implemented and documented for the Smart PDK September 14 Release 5.1.4 version. The following DRCs are implemented in the SMART Photonics PDK.

- All the design rules mentioned in SMART Photonics design manual are implemented in the SMART Photonics PDK except the rule ISO.0.1 is not implemented, whereas the length of cblsolation is required to be larger than 10.0 um.

- For ``WG.0.2|0.3|0.4``, additional warning for DFM values can be switched on by define "WG\_WARNING\_SMART".

- DRC of ``WG.0.7|0.8`` is only enabled by defining "EXTRA\_DRC\_SMART".

- DRC for ``bounding boxs overlapped`` is enabled to check if cells with bounding boxs overlap

with each other or not.

- DRC for ``Waveguide/text too close to the building block outline`` is enabled to check if there is minimum space between waveguide or text to the building block outlines.

#### Report Summary (WP3.4.DF.R0): Design Flow Document

#### Summary

This document describes the design flow from general idea to actual PICs (Photonic Integrated Circuits). First, there is not ONE design flow that fits all. Dependent on the application different design flows are used. On top of that, through time, there is an evolution of the design flow. This document will have the view that the Photonic Design Automation (PDA) design flow evolution will follow a similar evolution as of the Electronic Design Automation (EDA) design flow. The document will be used to identify the areas for improvement for the PDA design flow. It is also recognized that in many aspects the PDA design flow will have its own challenges unknown to the EDA design flow.

#### Work Package 4 – Process Improvement

#### Milestone (WP4.M5.1): AZ resist process development on PAS 2500/40 stepper Summary

In this report the optimal exposure settings of AZ resist used on a PAS 2500/40 stepper has been presented. In the current generic process to produce optical chips we still make use of contact exposure. Because of the contact between mask and wafer this technique is sensitive to defects (damaged wafers and mask wear). From a production point of view one would rather use projection exposure as it is a contactless way of exposing optical resist. Particles or defects that are present on the mask will be reduced in size on wafer level and there is hardly any mask wear. The available tool in the NanoLab@TU/e cleanroom for projection exposure is the PAS

Open Innovation Photonic ICs - Technical Summary Report

2500/40 Stepper from ASML and the resist of choice for process development on this tool is AZ4533.

Based on the FEM experiments performed on the AZ4533 resist with the PAS 2500/40 stepper the optimal exposure energy is set to 400mJ and the optimal focus depth is set to -1 micron. Based on these settings, wafer critical dimension uniformity measurements show the following values based on 246 measurements: the values are respectively 1531nm (+/-64nm) for top and 1579 (+/-68nm) for bottom. The loss of width, because of overexposure, needs to be taken into account at mask design level.

#### Outlook

The plan for the next reporting period will be briefly outlined here. With respect to meeting market demands, we will focus on creating a roadmap that will help aligning better the technical developments with actual market requirements. On the process characterization side measures that increase process maturity will be implemented such as tiling and novel passivation schemes. In addition new process building blocks such as semi-insulating substrate or more effective EO materials will be made available. First results will also be available for the novel building blocks and significant improvements will be done on the design environment. Furthermore, Technobis and Effect Photonics are working on the demonstrator designs and finally multiple highlights in the area of process development such as processes for high-speed RF lines and Al-based modulators will be released.

Partners

### **Open Innovation Photonic ICs OpenPICs Technical Summary Brief** (01/2018 - 07/2018)

#### **Table of Contents**

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| WORK PACKAGE 1 – MARKET DEMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2  |

| Milestone Summary (WP1.M3): Platform Roadmap<br>Milestone Summary (WP1.M4): Key Performance Indicators for MPW Runs (KPIs)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| WORK PACKAGE 2 – PROCESS CHARACTERIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3  |

| Milestone Summary (WP2.1-M1.3): Generic MPW Data - Update June'18<br>Note on Milestone WP2.2-M2.2 Dummy Structures / Tiling<br>Milestone Summary (WP2.3M1.2): Semi-Insulating Substrate                                                                                                                                                                                                                                                                                                                                                                                    |    |

| WORK PACKAGE 3 – BUILDING BLOCK IMPROVEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4  |

| Milestone Summary (WP3.1.M0): Technology and Design Concept - Laser<br>Report Summary (WP3.1.R0): Mask Design Tape-out, Analysis and Design - Laser<br>Milestone Summary (WP3.1.M1): Mask Design Tape-out I - Laser<br>Report Summary (WP3.1.R1): Building Block Results I - Modulator<br>Milestone Summary (WP3.3.M0.IT0): Report on Standard MPW BB Cell Results<br>Milestone Summary (WP3.3.M0.IT1): Report on Standard MPW BB Cell Results<br>Milestone Summary (WP3.4.DF.M1): Design Flow Improvements<br>Report Summery (WP3.4.DRC.R2): DRC Implemented Improvements |    |

| WORK PACKAGE 4 – PROCESS IMPROVEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7  |

| Milestone Summary (WP4.MS2.1): Investigation of Zn-diffusion for MPWs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| <b>CO</b> Confidential, only for members of the consortium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | СО |

#### Introduction

This summary brief will give an overview of the activities carried out in the first half of 2018 within the Open Innovation Photonic IC project. The activities are divided between four work packages: Market Demand, Process Characterization, Building Block Improvement and Process Improvement. Significant progress has been made in WP1 through the release of a platform roadmap, defining the state-of-the-art of open access generic photonic integration platforms based on InP and SiNx, and presenting the technology projections for the coming 2-5 years. It has been distributed in three major conferences this year already. In addition, key performance indicators of the multi-project wafer runs (MPW) have been gathered to better understand the operational aspects of the open access runs. More than 100 designs have been prototyped alone in the last two years. In WP2, the Smart Photonics foundry has made progress in implementing characterization and monitoring methods so that the pilot manufacturing line performance and stability can be accurately tracked. This will help in achieving reproducible wafers and devices. Metrics such as laser threshold current, series resistance are being tracked in addition to optical loss and waveguide dimensions. In WP3, steady work on building block development has been performed, e.g. the fabrication of DBR laser modules with several mW output power and the demonstration of fast optical modulators exceeding 20 Gb/s. In addition, building block test structures for PDK data generation have been revised and periodically added to MPW runs. In WP4, an interesting process to fabricate low-loss optical waveguides has been trialled and investigated in-depth, yielding useful insight to future process improvements. More details on the activities in each WP are given below.

#### Work Package 1 – Market Demands

#### Milestone Summary (WP1.M3): Platform Roadmap

This initiative was coordinated by JePPIX and driven by all the partners of the JePPIX open access technology platforms in InP and SiNx. It represents the current development of such technologies, reports the market analysis of photonics integration, shows the analysis of each part of the value chain on the ecosystem and the projections on new technology nodes for photonic integration technology.

The 2018 roadmap synthesizes JePPIX's analysis of the PIC market and market requirements for the coming 2-5 year timescale. Important technology developments required to foster the foreseen market growth are analysed in many areas, including fabrication processes and equipment, design software, packaging and testing.

As part of the dissemination activities of WP1, a publicity campaign was performed to disseminate the JePPIX roadmap 2018. The campaign included:

- Release of a bulletin <u>https://mailchi.mp/a47397a9c0b9/jeppix-bulletin-april-2018</u> (369 opens)

- 100 USB stick with the roadmap distributed at OFC 2018

- Announcement in LinkedIn (49 likes, 266 views), e-broadcast (>400 people)

- JEPPIX webpage with link to download (980 views, 249 downloads)

http://www.jeppix.eu/vision/

- Interview in Photon Delta website (1797 views) <u>https://www.photondelta.eu/news/insights/jeppix-launches-2018-roadmap-at-ofc/#sthash.875UzhSc.dpbs</u>

- WTMF copies of Roadmap (50 copies)

- IPRM/CSW Boston (20 copies)

#### Milestone Summary (WP1.M4): Key Performance Indicators for MPW Runs (KPIs)

Open access technology platforms exist as a solution for PIC prototyping on a fab-less lab-less model. They provide cheap fabrication entry costs and a relatively simple chip design process for first entry designers. The value of MPW runs translates into innovative application fields and improvement of performance of the current building blocks. In order to retrieve valuable information to analyse and overcome KPIs challenges valorisation methods are needed. Within WP1 different approaches to gather crucial information on the technology have been implemented. First in order to bridge the gap between technology development and commercially available products we have generated several reports "linking BB to products". In this way we are able to analyse both, the real necessities of a company to create a prototype and the needs of the current photonic components to perform as required by the industry.

Another approach we took is gathering valuable information from previous MPW run users both from the public and private sector. This action allows us to evaluate the performance of the complete value chain of open access technology platforms and offer the required information to run the adequate root-cause methodology in each part of the value chain (administrative process, BB development & performance, software, design and packaging). The results of this analysis are fed back to each part of the ecosystem.

The activities of WP1 during the first half of 2018 focused on 2 parts: one, the methodology of acquiring clients, where we have been tracking the procedure of acquiring or starting new projects that lead to an MPW run. This activity aims to increase the number of effective leads and to provide broad dissemination and feasibility support for PICs to first entrance users in different application fields. Second, since August 2017 we worked on creating the JePPIX roadmap 2018. This roadmap is a breakpoint in the technology development and represents the photonic integration ecosystem. This roadmap serves as a guideline to the PIC market; moreover, JePPIX members are also contributing to the AIM road mapping initiative led by MIT and the World Roadmap for Integrated Photonics, led by Photon Delta.

### Work Package 2 – Process Characterization Milestone Summary (WP2.1-M1.3): Generic MPW Data - Update June'18

#### Goals

Improve stability of the Equipment and Processes as used in the MPW. *Achievements*

Stability improvements have been introduced throughout the Smart Photonics line. The introduction of the Passivation and Polyimide improvements in SP19 and SP20 have resulted in a further reduction of Threshold Currents in SP21 to below 25mA/mm for All Active FP lasers.

The epitaxy department has introduced a higher number of calibration runs that guarantee a much more controlled PL on released wafers.

And the MPW introduction of 193nm Scanner lithography has made a large improvement on Waveguide Line Width control. Standard deviations for Waveguides have been reduced from circa 6% to below 1% (1sigma).

#### Note on Milestone WP2.2-M2.2 Dummy Structures / Tiling

The implementation of Dummy Structures and Tiling Density has been delayed to MPW SP24B for the July 2018 Tape-Out

### Milestone Summary (WP2.3.-M1.2): Semi-Insulating Substrate

#### Goals

Verify basic MPW performance when using Semi-Insulating substrates in the MPW B-runs.

#### Achievements

Performance parameters for Semi-Insulating (SI) substrates were similar to the standard MPW process parameters on S-doped InP. Deep waveguide losses below 3dB/cm and laser threshold currents below 25mA/mm with 0.15 slope efficiency have been measured. As expected, only a slight increase of the series resistance of almost 3 Ohms has been observed. Offering SI-substrates and processing is therefore considered to be low risk.

#### Work Package 3 – Building Block Improvement

#### Milestone Summary (WP3.1.M0): Technology and Design Concept - Laser

In this milestone we present specifications of the tuneable lasers defined by Technobis for use in their demonstrator. We examine different tuneable laser geometries and present their stateof-the-art properties. The specifications of these lasers define the required technology. We consider the Indium Phosphide (InP) technology platform provided by Smart Photonics and the silicon nitride (SiN) technology platform provided by Lionix International (TriPleX) for development of the low linewidth laser.

**Report Summary (WP3.1.R0): Mask Design Tape-out, Analysis and Design - Laser** In this document we presented design considerations for the DBR test structures and DBRbased tuneable lasers. In order to use DBR gratings in various systems (lasers, filters or others) designers should be able to predict the performance of gratings using theoretical models. A prerequisite to accomplish this is that the behaviour of the gratings for different geometries (pitch, length and strength) should be properly characterized. A next step is to compare measurements with simulation results. However, adequate characterization of the grating is not a simple task. The experimental results are influenced by the accuracy of the fabrication as well as accuracy of measurements itself. For Smart Photonics MPW run 20 we prepared a series of DBR grating test structures which allow to:

Determine the deviation of the spectral response of the gratings vs. geometry.

- Define a deviation of the effective index of the grating. This is necessary to have a link between the pitch and peak of the reflection band of the DBR grating.

- Choose an optimal method to obtain the absolute reflection spectra of the gratings. This can be used later on to characterize DBR gratings fabricated using scanner technology.

- Compare experimental and simulation results.

Moreover, the mask design includes test structures of various tuneable DBR-based lasers. Characterization of these tuneable lasers is a first step to include them into a library, e.g. the Smart Photonics PDK. Moreover, the results obtained from the characterization of these lasers will help in considerations for the other tuneable laser designs, namely hybrid low-linewidth laser and widely tuneable laser based on sampled gratings.

#### Milestone Summary (WP3.1.M1): Mask Design Tape-out I - Laser

We have designed a mask for examining performance of the DBR gratings (spectral response) and DBR based tuneable lasers. The results obtained after measurements of the test structures will:

- Allow quantification of DBR spectral response variation in gratings of the same pitch and length. This information is highly valuable for the PIC designers who are willing to use DBR gratings in tuneable lasers and for filtering purposes;

- By comparing measurements of the different test structures we can establish most reliable characterization technique, which in its turn can be used later on to characterize gratings fabricated using scanner lithography;

- Measurement results can be used to calibrate grating models, which can be included in the building block modules in circuit simulators.

Basic measurements of tuneable DBR lasers, e.g. LI curves, tuneability, and SMSR, will provide a quick indication of laser performance. In case the performance of the lasers is acceptable, i.e. a power >1 mW, and a SMSR>25 dB, these tuneable single mode lasers can be added to a library for the Smart Photonics process. In addition to this more advanced measurements on for example wavelength stability and RIN (noise) can be performed.

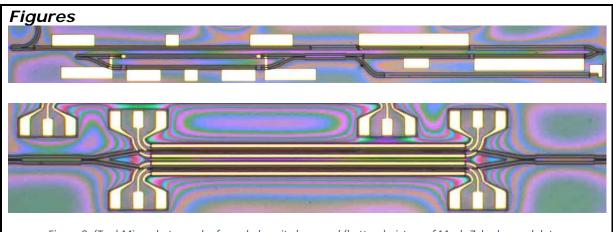

#### Report Summary (WP3.1.R1): Building Block Results I - Modulator

MZ modulator chips were fabricated in the SP20 B run and have been characterized with respect to their electrical and electro-optical behavior. The electrical results indicate a bandwidth of around 30 GHz. The measurements support and strengthen the insights gained from the simulations on the effect of geometrical parameter variation on modulator performance. The electro-optic large signal modulation experiments show only open eye diagrams until 20 Gb/s which is surprising given the measured bandwidth. Several possible causes have been suggested and further investigation is needed to determine the exact reasons.

#### Milestone Summary (WP3.3.M0.IT0): Report on Standard MPW BB Cell Results

One of the project's goals is to enrich the process design kit (PDK) of the regular multi-project wafer runs (MPW). For this reason test structures have been designed that contain basic building blocks (BBB) which are fabricated in each run, so that their performance can be

characterized. This will feed back to the improvement of the PDK. Among those test cells, there are also lower level test structures that assess more fundamental parameters of a MPW such as metal or planarization properties. Those are equally important for the PDK, especially for developers of more advanced components. In this report, we present measurement results of low-level test structures from MPW SP19 and SP21. It establishes design rules for small metal features and also presents their sheet resistance and RF behavior for either sputtered or electro-plated processes. In addition, the p-InP sheet resistance has been measured and planarization of polyimide on shallow and deep trenches was investigated. Further results on the contact resistance measurement structures are to be expected soon for other MPW runs and more insight into the planarization topology is expected.

#### Milestone Summary (WP3.3.M0.IT1): Report on Standard MPW BB Cell Results